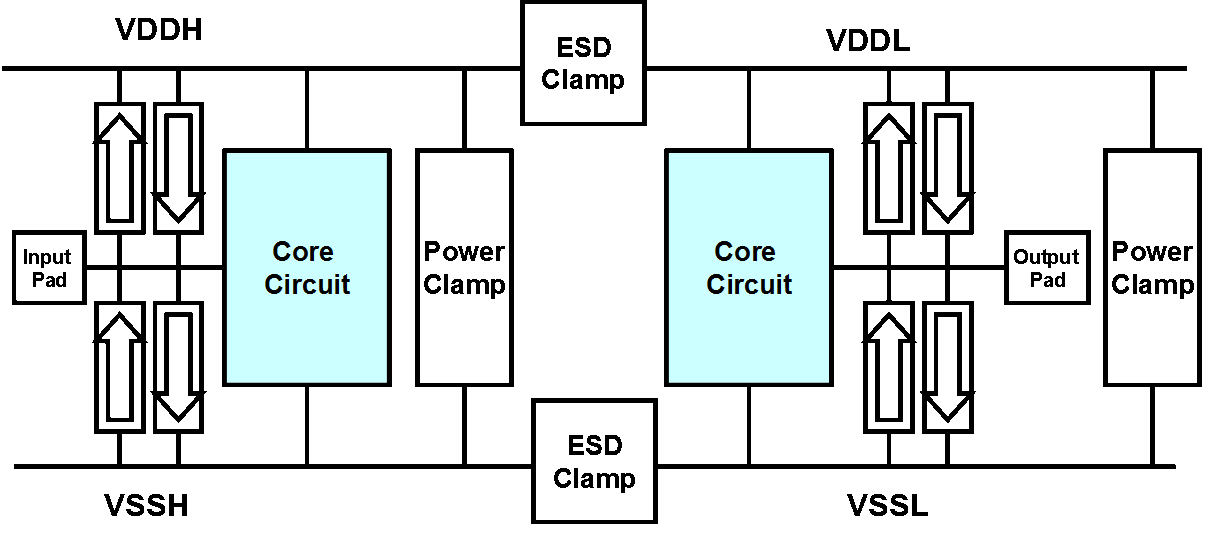

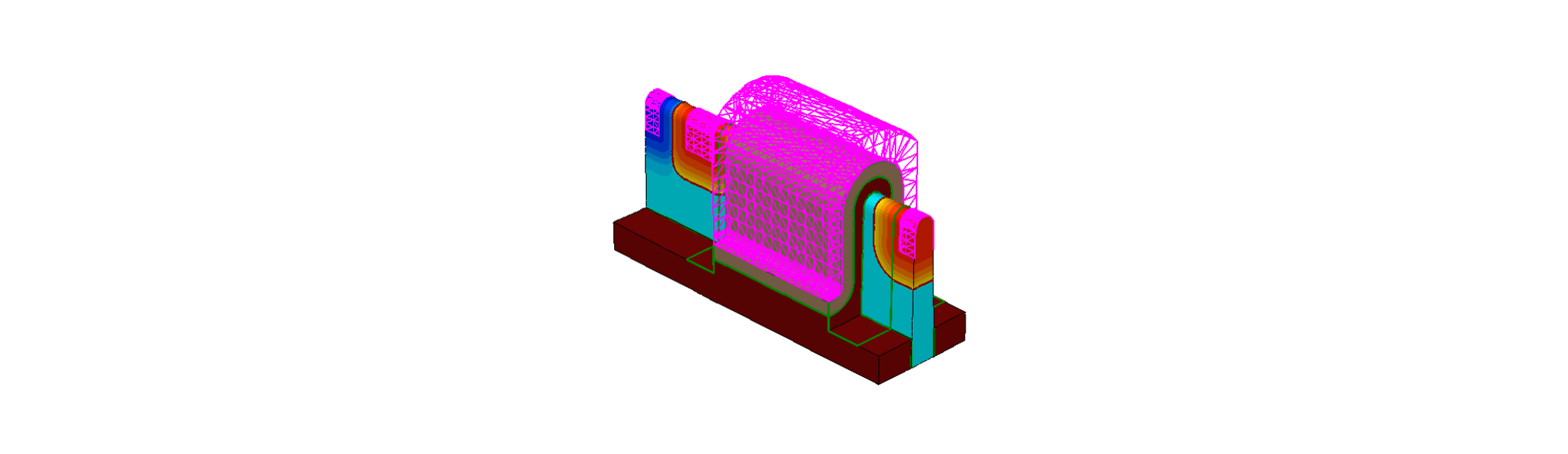

整體靜電防護方案可為多個技術節點中的集成電路提供有效的靜電防護。所用保護器件以基於TCAD的器件與工藝仿真進行設計與驗證。這些器件可應用在IO的靜電防護電路和電源箝制電路中。所開發的靜電保護方案能提供高達8000V的人體放電模型(HBM)保護,除去電源閂鎖效應。提供靜電防護器件的集約模型可與核心電路一起進行快速高效的靜電防護仿真。

- 0.5 um 200V SOI BCD 工藝完整解決方案 (HBM 2000V)

- 0.35 um CMOS工藝完整解決方案(HBM 4000V)

- 0.13 um CMOS工藝完整解決方案(HBM 2000V)

- 65 nm CMOS工藝完整解決方案(HBM 2000V)

- 55 nm CMOS工藝完整解決方案(HBM 8000V)

- 40 nm CMOS工藝完整解決方案(HBM 2000V)

- 16 nm CMOS工藝完整解決方案(HBM 2000V)